Table of Contents

This article has been submitted by a user. Unfortunately he is not able to verify that the example is running.

Therefore it cannot be considered as working.

Another Microblaze eample can be found at MicroBlaze MCS Demo

"Hello World!" running on Microblaze

Ths project implements a Microblaze Soft Processor with a “Hello Wold!” example software running on it. It was tested on successfully on ZTEX USB-FPGA-Modules 1.11c.

The project sources can be downloaded by clicking on tho following link: Microblaze Hello World Example.

License requirements: you'll need Xilinx EDK license (not free one) to be able to use XPS/SDK components, ISE require WebPACK license (free one).

Project Overview

FPGA board specific constraints are defined in resetClockTrace.ucf (reset and clock signals) and ddr-sdram-simon.ucf (DDR SDRAM signals).

The Microblaze soft processor core was generated using the ISE/XPS “embedded processor” Wizard (configuration stored in processor/processor.mhs).

The software is defined in processor/SDK/SDK_Workspace_32/hello_world_0/src/helloworld.c. At startup the XilKernel is launched and a static thread

sending “Hello World” to default UART port configured at the moment “embedded processor” is created.

Implementing the Design / Generating the Bitstream

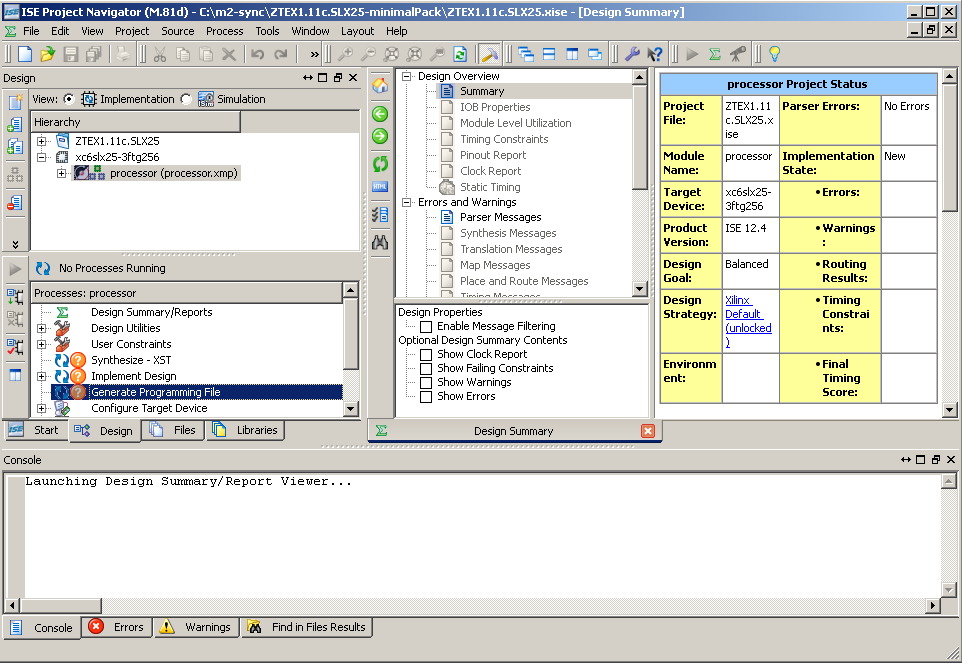

In order to implement the design just open ZTEX1.11c.SLX25.xise project file, select “processor” entity and double click on “Generate Programming File”.

From ISE project page double click on processor.xps file in order to launch Microblaze designer (Xilinx Platform Studio). XPS will provide all components connectivity within PLB bus and external pins management.

Compiling the Software

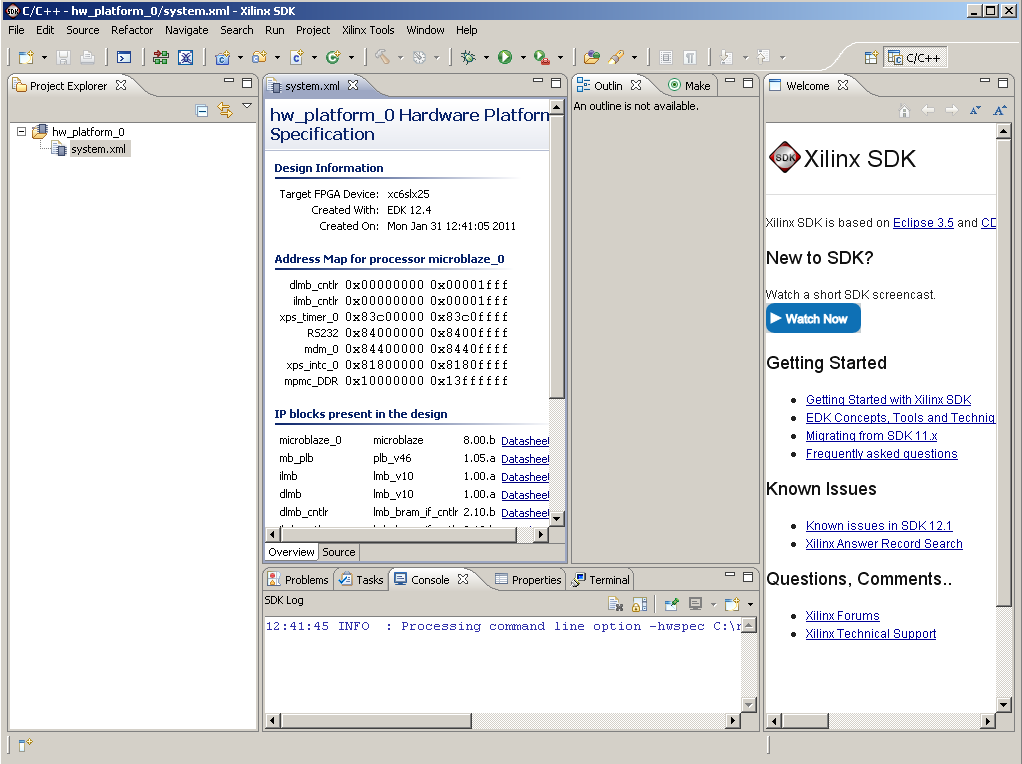

From XPS project page choose top menu Project→“Export Hardware Design to SDK in order to launch Microblaze SDK (Eclipse based environment).

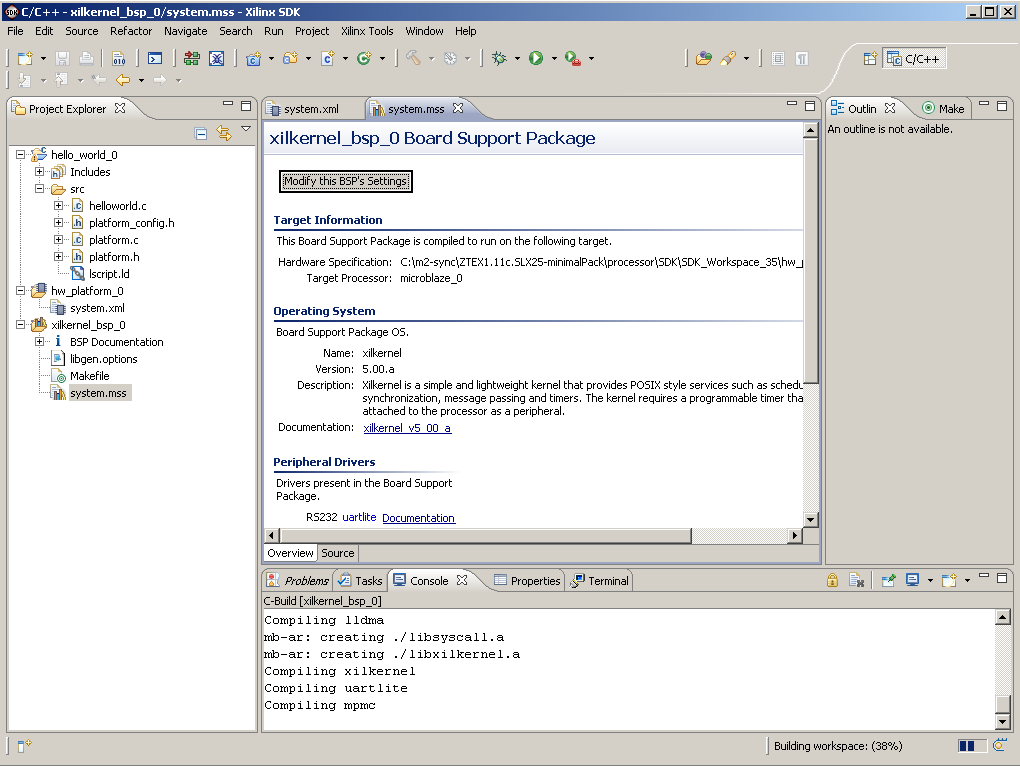

SDK will provide all software integration including HAL definition (hw_platform_0) and BSP functionality (xilkernel_bsp_0).

(use File→Import→General→Existing projects into Workspace to obtain all predefined components)

Running the example

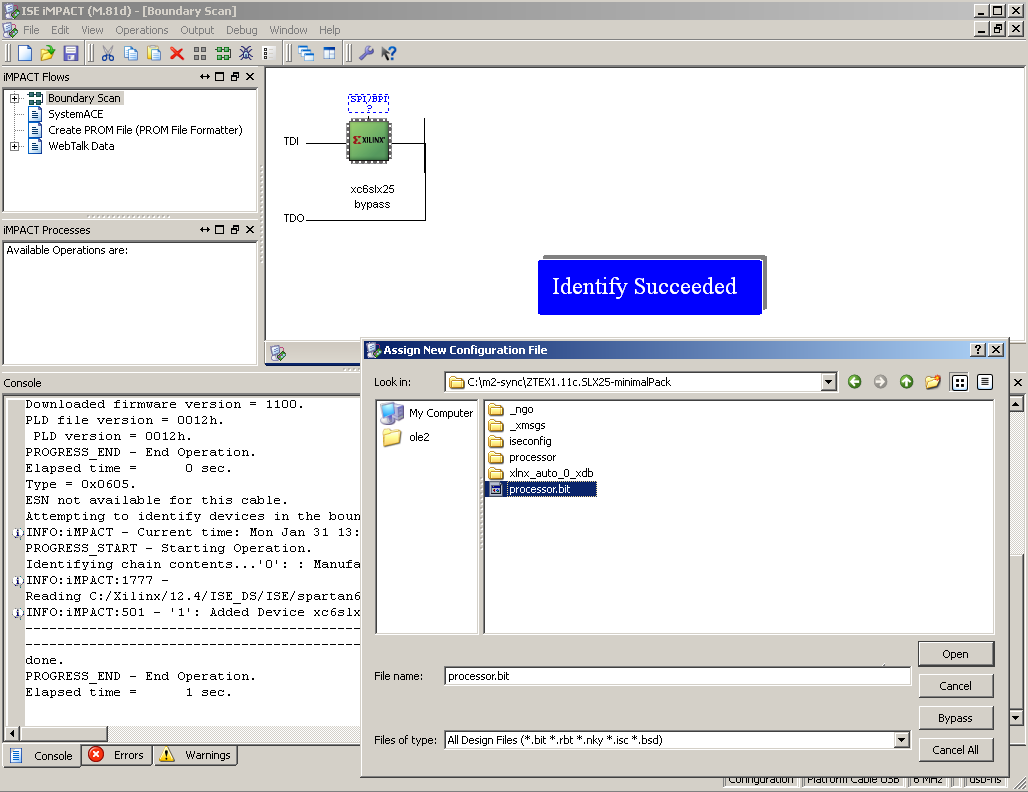

The Bitstream can be uploaded via JTAG either using the Impact tool

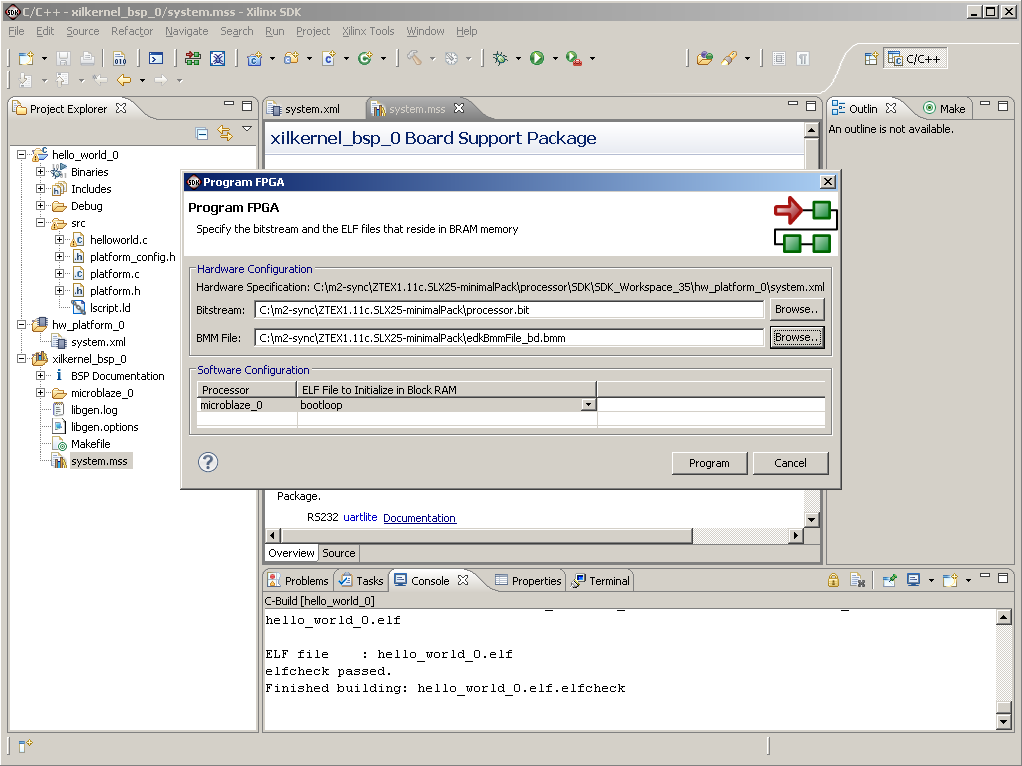

or the Program FPGA dialog of the Xilinx SDK.

It is also possible to upload the Bitstream via USB using the Java API or using FWLoader of the ZTEX SDK package:

FWLoader -c -uu standalone.ihx -um processor.bit

(Since no special firmware for the EZ-USB is required standalone.ihx from the standalone example of the ZTEX SDK can be used as dummy firmware.)

The Microblaze Firmware (“Hello World” example) can be started from SDK after uploading the Bitstream. (step on project folder hello_world_0 and use menu Run→Run As→Launch on Hardware)

In order to run or at least to program .elf into the board bootloop.bmm (aka edkBmmFile_bd.bmm) must be uploaded first into BRAM block. This bootloader accept .elf binary delivered by JTAG interface and provide necessary environment for correct launch it.

It is also possible to include bnm files (that are files are BRAM images) into bitstream using he data2mem tool from Xilinx (<bit file> + <bmm file> = <new bit file>, where <new bit file> can be uploaded directly using FWLoader.