Table of Contents

Porting to USB-FPGA Modules 1.15y

In order to simplify the porting of applications from USB-FPGA Modules 1.15d and 1.15x to USB-FPGA Modules 1.15y the FPGA Boards are designed to be as compatible as possible.

FPGA

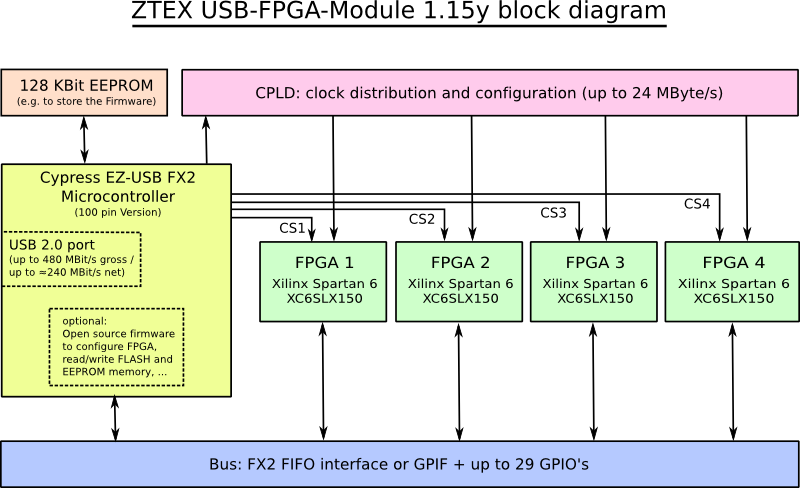

The I/O signals of the EZ-USB FX2 micro controller are shared by all FPGA's. These signals form a bus which is controlled by the FX2 USB controller using chip select (CS) signals. This is depicted in the USB-FPGA Module 1.15y block diagram:

In order to ensure signal quality all clock signals are distributed using the CPLD.

The following checklist contains things that have to be considered for porting the HDL code

- Implementation of the CS signal (ball AB11): Inputs are valid if CS is high; outputs are only driven is CS is high

- FPGA to FX2 connection are the same with the following exceptions / limitations (see List of Connections for details):

- IFCLK (Ball K20) must not be used as output

- Ball W17 (CCLK during configuration) must not be used as output

- Location of signal PA4 is different (AB21 instead of W17)

- CTL5 is not available

- Unused I/O's that are connected to FX2 outputs must float. This also includes I2C signals. It is recommended to let all unused I/O's float.

- The FPGA number can be determined using balls T17, R13 and T12

Firmware

The EZ-USB controls the FPGA communication using the CS signals. These signals are implemented in the Firmware Kit of the SDk and can be controlled by the host software. In simplest case only the FPGA board identification macro has to be changed (to “IDENTITY_UFM_1_15Y(…);” )

For more complex applications the following methods, macros and variables are available.

Variables:

__xdata BYTE select_num; // currently selected FPGA __xdata BYTE prev_select_num; // previously selected FPGA

The Macro PRE_FPGA_SELECT is called between deselection and selection of a FPGA. Typically it is used to sore / restore IO states. The following example saves IOC state for previously selected FPGA and restores the IOC state for the newly selected FPGA.

#define[PRE_FPGA_SELECT][PRE_FPGA_SELECT OLD_IOC[prev_select_num] = IOC; IOC = OLD_IOC[select_num]; ]

The method

void select_fpga ( BYTE fn )

can be used to select an FPGA. In particular this method

- set

prev_select_num = select_num; select_num = fn; - deselect previous FPGA

- calls macro

PRE_FPGA_SELECT; - select new FPGA.

Host software

The host software API contains two methods for multi-FPGA boards:

int numberOfFpgas(): returns number of FPGA'svoid selectFpga(int num): Selects a FPGA. This calls theselect_fpgamethod of the firmware.

Examples

Simple examples can be found is the SDK package. A more complex application (which uses the PRE_FPGA_SELECT macro is BTCMiner.